Product Summary

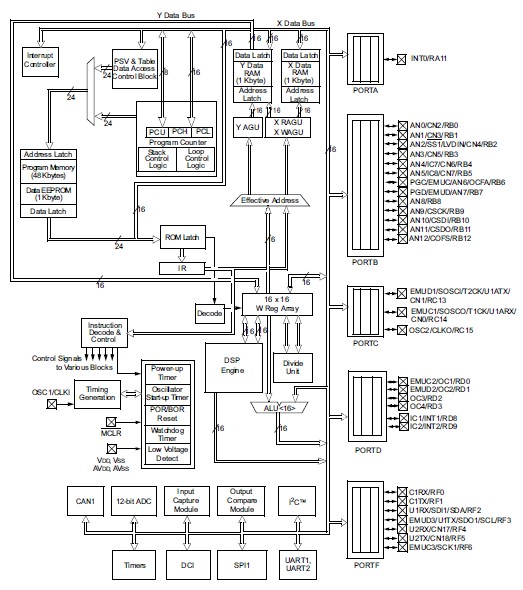

The DSPIC30F4013-30I/P is a high-performance digital signal controller. The DSPIC30F4013-30I/P devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture.

Parametrics

DSPIC30F4013-30I/P absolute maximum ratings: (1)Ambient temperature under bias: -40℃ to +125℃; (2)Storage temperature: -65℃ to +150℃; (3)Voltage on any pin with respect to VSS (except VDD and MCLR)(Note 1): -0.3V to (VDD + 0.3V); (4)Voltage on VDD with respect to VSS: -0.3V to +5.5V; (5)Voltage on MCLR with respect to VSS: 0V to +13.25V; (6)Maximum current out of VSS pin: 300 mA; (7)Maximum current into VDD pin (Note 2): 250 mA; (8)Input clamp current, IIK (VI < 0 or VI > VDD): ±20 mA; (9)Output clamp current, IOK (VO < 0 or VO > VDD): ±20 mA; (10)Maximum output current sunk by any I/O pin: 25 mA; (11)Maximum output current sourced by any I/O pin: 25 mA; (12)Maximum current sunk by all ports: 200 mA; (13)Maximum current sourced by all ports: 200 mA.

Features

DSPIC30F4013-30I/P features: (1)Enhanced Flash program memory: - 10,000 erase/write cycle (min.)for industrial temperature range, 100K (typical); (2)Data EEPROM memory: - 100,000 erase/write cycle (min.)for industrial temperature range, 1M (typical); (3)Self-reprogrammable under software control; (4)Power-on Reset (POR), Power-up Timer (PWRT)and Oscillator Start-up Timer (OST); (5)Flexible Watchdog Timer (WDT)with on-chip low power RC oscillator for reliable operation; (6)Fail-Safe Clock Monitor operation: - Detects clock failure and switches to on-chip low power RC oscillator.

Diagrams

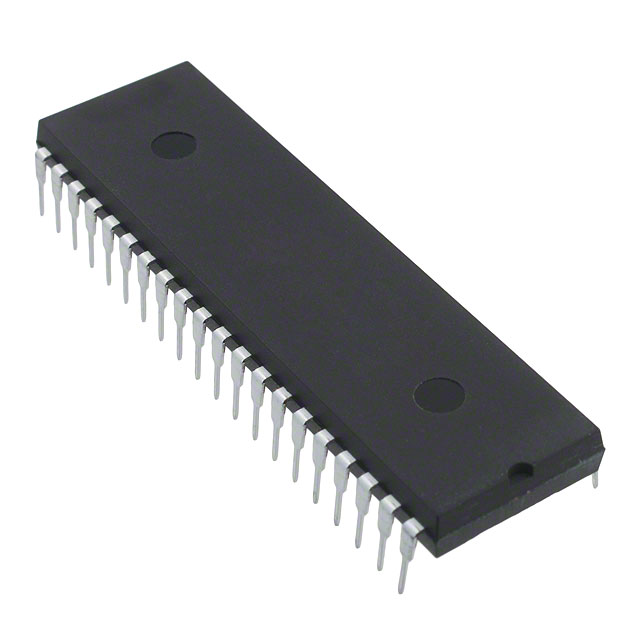

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

DSPIC30F4013-30I/P |

Microchip Technology |

Digital Signal Processors & Controllers (DSP, DSC) General Purpose |

Data Sheet |

|

|

||||||||||||

|

DSPIC30F4013-30I/PT |

Microchip Technology |

Digital Signal Processors & Controllers (DSP, DSC) General Purpose |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))