Product Summary

The LP621024DM-70LL is a low operating current 1,048,576-bit static random access memory organized as 131,072 words by 8 bits and operates on a single 5V power supply. Inputs and three-state outputs of the LP621024DM-70LL are TTL compatible and allow for direct interfacing with common system bus structures. Two chip enable inputs are provided for POWER-DOWN and device enable and an output enable input is included for easy interfacing. Data retention of the LP621024DM-70LL is guaranteed at a power supply voltage as low as 2V.

Parametrics

LP621024DM-70LL absolute maximum ratings: (1)VCC to GND: -0.5V to + 7.0V; (2)IN, IN/OUT Volt to GND: -0.5V to VCC + 0.5V; (3)Operating Temperature, Topr: 0 to + 70℃; (4)Storage Temperature, Tstg: -55 to + 125℃; (5)Temperature Under Bias, Tbias: -10 to + 85℃; (6)Power Dissipation, PT: 0.7W; (7)Soldering Temp. & Time: 260℃, 10 sec.

Features

LP621024DM-70LL features: (1)Single +5V power supply; (2)Access times: 55/70 ns (max.); (3)Current: Very low power version: Operating: 70mA (max.); Standby: 25μA (max.); (4)Full static operation, no clock or refreshing required; (5)All inputs and outputs are directly TTL-compatible; (6)Common I/O using three-state output; (7)Output enable and two chip enable inputs for easy application; (8)Data retention voltage: 2V (min.); (9)Available in 32-pin DIP, SOP TSOP and TSSOP (8 X 13.4mm) packages.

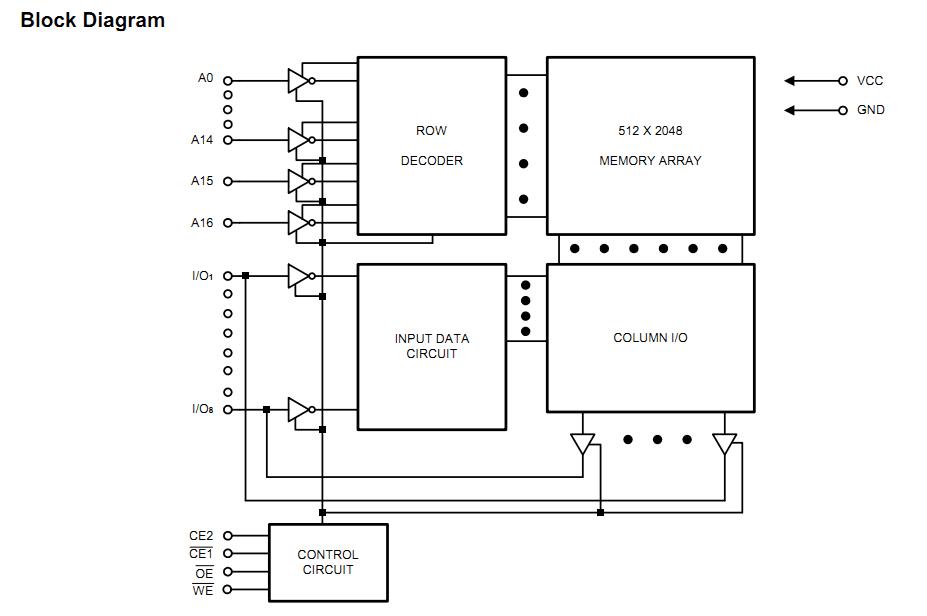

Diagrams

|

LP621024D |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LP621024D-I |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LP621024D-T |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LP621024E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LP621024EI |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

LP62E16128A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))